Clock Drivers & Distribution ISP 0 Delay Unv Fan- Out Buf-Sngl End I

Die Bilder dienen nur als Referenz.

Produktdetails finden Sie in den Produktspezifikationen.

Clock Drivers & Distribution ISP 0 Delay Unv Fan- Out Buf-Sngl End I

Bei Bestellungen über 200 $ besteht Anspruch auf ein Geschenk im chinesischen Stil in limitierter Auflage.

Bei Bestellungen über 1.000 US-Dollar entfällt die Versandkostenpauschale in Höhe von 30 US-Dollar.

Bei Bestellungen über 5.000 US-Dollar entfallen die Versand- und Transaktionsgebühren.

Diese Angebote gelten sowohl für Neu- als auch für Bestandskunden und sind vom 1. Januar 2024 bis 31. Dezember 2024 gültig.

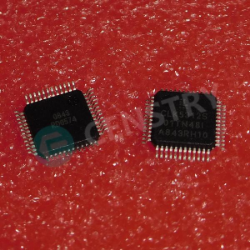

Lattice

ISPPAC-CLK5312S-01TN48I datasheet

QFP-48

Clock & Timer IC

Senden Sie jetzt Ihre Angebotsanfrage und wir erwarten, dass wir Ihnen innerhalb von 24 Stunden ein Angebot unterbreiten Mai 03, 2024. Geben Sie jetzt Ihre Bestellung auf und wir gehen davon aus, dass die Transaktion innerhalb dieser Frist abgeschlossen wird Mai 08, 2024. Ps: Die Zeit entspricht GMT+8:00.

Lattice

3982 PCS

MXO1200C-3MN2C .PDF

Lattice

1 PCS

MC68360AI25VL .PDF

Lattice

159 PCS

MANO MLV5 .PDF

Lattice

138 PCS

MACH435Q-20JC .PDF

2024-05-02

very fast thanks

2024-05-02

Fast shipping

2024-05-02

Goods arrived and work perfectly.

2024-05-01

impossible to find, except here.

2024-04-30

TRANSISTORS ARE GOOD

2024-04-27

Mercancía correcta. Envío rápido. Muy satisfecho.

2024-04-22

Censtry elec = Good company, happy business

2024-04-11

We highly recommend Pinewood Electronics Ltd and are looking forward to our next deal. Darren is very professional and our order was shipped promptly and the parts were good quality.

2024-03-21

Good supplier !i will buy it again ,Nice

2024-02-07

Very proffessional and reliable company. Was a pleasure for me to work with Mara.

Wir legen großen Wert auf Ihr Feedback. Bitte teilen Sie uns Ihre authentischste Bewertung mit.

*Melden Sie sich bitte an, um einen Kommentar zu veröffentlichen